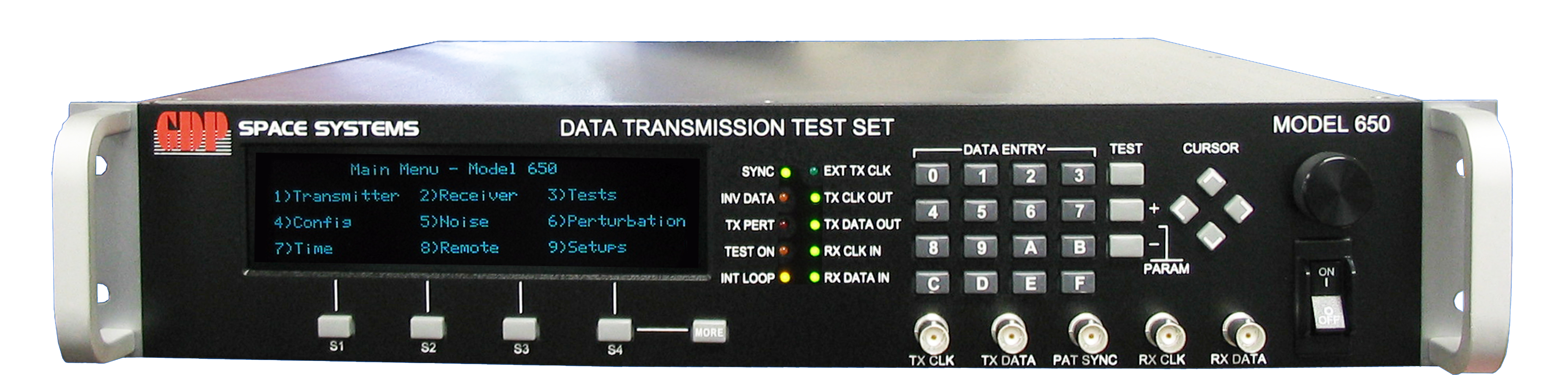

Data Transmission Test Set w/ BERT

The GDP Model 650 Data Transmission Test Set fills the need for data-link verification and qualification at an affordable price. The user is provided with totally independent transmit and receive functions to allow rapid fault isolation and data link characterization. Simulated signal perturbations are created programmably by adding noise, baseline offset, missing bits, bit -rate jitter and varying signal levels. Features such as an internal 6-digit frequency synthesizer and IRIG Code generator and converter make the Model 650 especially suited to the test and evaluation of PCM Telemetry data link systems and components.

The Model 650 provides measurement capability for: Accumulated Bit Errors, Measured Bit Error Rate, Elapsed Test Time, Accumulated Errored Seconds, Errors per Second, Measured Error Symmetry, Accumulated Bit Count Integrity Loss (Bit Slips), Measured Transmit and Receive clock rate.

Operating ease and test flexibility is the result of using microprocessor control to augment high speed hardware functions. A high contrast vacuum fluorescent display provides setup and test result information in easy-to-use formats.

1 bps to 36 Mbps Operation (Standard)

- 1 bps to 50 Mbps Operation*

Independent Transmitter & Receiver

Measures: Bits, Seconds, Bits in Error, Seconds in Error, Bit Error Rate (instantaneous and average)

Data Symmetry & Bit Slip Tests

TX & RX Frequency Measurement

16 PRN Sequence Codes Forward & Reverse 2n-1, n= 5, 7, 9, 11, 15, 20, 23, 31 (Forward or Reverse) and User Defined Taps on 31-bit Register

Fixed Programmable Data Patterns 8, 16, 32, 64, 128, 256-bit or Dotting

Internal DDS Frequency Synthesizer

– IRIG Code Generation and Conversion

Additional Features

Randomizer / Derandomizer (Fwd & Rev)

IRIG (215-1), 29-1, 211-1, 217-1, 223-1, V.35, V.36

Convolution Encode / Decode

TTL, Bipolar, RS-422 Signal Interfaces

Remote Control / Monitor: Ethernet

Internal Noise Source*

- Programmable Eb/No and Signal Level

Automatic Eb/No Test

Analog Signal Output Interface*

Acquisition Time Test*

Jitter Test*

Link Delay Test*

* optional

Functional Description

A modular architecture gives the Model 650 superior flexibility. A fully programmable frequency synthesizer allows transmit clock generation from 1 bps to 50 Mbps with 6-digit resolution. A flexible interface structure, which provides IRIG code converters for both input and output data, allows the Model 650 to fully support test and evaluation of telemetry receive and processing systems.

The BER (Bit Error Rate) Module is the major functional element in the Model 650. A microprocessor resident on the BER module controls the BERT transmit and receive circuits through user commands issued from the local front panel or remote control port. Communication between the microprocessor module and the BER module is accomplished using semaphores passed into a dual-port RAM architecture.

All high-speed functions, such as data generation, PRN correlation, error detection, and accumulation, are performed by hardware. Low-speed functions, such as test data accumulation and formatting for the front panel and remote monitoring ports, are provided by the embedded

Applications

DATA LINK TESTING

In a telemetry ground station or in a satellite ground data handling system, the Model 650 provides the capability to perform data-link quality analysis and overall system checkout. A single Model 650 provides independent data transmit and data receive circuits to support loop-back verification of a ground station.

The Model 650 is user-programmed for a variety of data patterns and bit rates. By utilizing appropriate connection points in the communications system, the entire data link is tested from the antenna through the bit synchronizer. Recovered data is synchronized by the Model 650 and test results are accumulated for user analysis.

BIT SYNCHRONIZER TESTING

The Model 650 provides high-performance functionality and ease-of-use in a single package. Using the internal (option) or external noise source with the adjustable Eb/No setup greatly simplifies Bit Sync Testing. These features, coupled withthe GDP VI Software, make the Model 650 an excellent addition to any telemetry system or Bit Synchronizer Test Station.

Ordering Options

Base

| Model 650 | Data Transmission Test Set with Bit Error Rate Tester (35 Mbps) Basic Unit provides:

|

| Model 650-OPT1 | Data Link Test Set with Bit Error Rate Tester (50 Mbps)- Including: IRIG Code Converter/Generator; Measured Accumulated Bit errors, Elapse test Time, Bits in Error, Seconds in Error, Bit error rate (Instantaneous and average); TX & RX Freq Measurements: Data Symmetry and Bit Slip test; Ethernet & RS232 Remote control and Option Package 1 >OPT1 Option Package Includes the Basic Unit plus the following option:

|

Options

| OP650-62 | Extended Bit Rate 50 Mbps |

| OP650-65 | Programmable Internal Noise Source |

| OP650-66 | B.S. Acquisition Time Test |

| OP650-67 | B.S, Jitter Measurement |

| OP650-68 | Link Delay Measurement Capability |

| OP650-89 | Chassis Slides |

| OP650-VI | Virtual Interface Remote SW |

| CAB650-01 | D to RS-422 Cable |

Option Descriptions

Explore the Model 650 option set designed to push data link testing beyond basic validation. With built-in noise generation, Eb/No control, and VI software automation, the Model 650 enables precise measurement of BER, jitter susceptibility, and link performance, helping engineers confidently verify real-world system behavior.

Send us your telemetry requirements!

Unlock precise data insights with our tailored telemetry solutions – send us your telemetry requirements today and elevate your business intelligence